Command Palette

Search for a command to run...

Google Enthüllt Seine TPU-Geheimwaffe, AlphaChip, Veröffentlicht in Nature! Detaillierte Analyse Der Entwicklungsgeschichte Von KI-Design-Chips

Im Jahr 2020 veröffentlichte Google ein wegweisendes Preprint-Papier mit dem Titel „Chip Placement with Deep Reinforcement Learning“, in dem es der Welt erstmals sein Chip-Layout vorstellte, das mithilfe einer neuen Methode des bestärkenden Lernens entworfen wurde.Diese Innovation ermöglichte es Google, KI in das Chipdesign von TPU einzuführen und so ein Chiplayout zu erreichen, das das von menschlichen Designern übertrifft.

Bis 2022 hat Google den im Dokument beschriebenen Algorithmuscode als Open Source freigegeben, sodass Forscher auf der ganzen Welt diese Ressource zum Vortrainieren von Chipblöcken nutzen können.

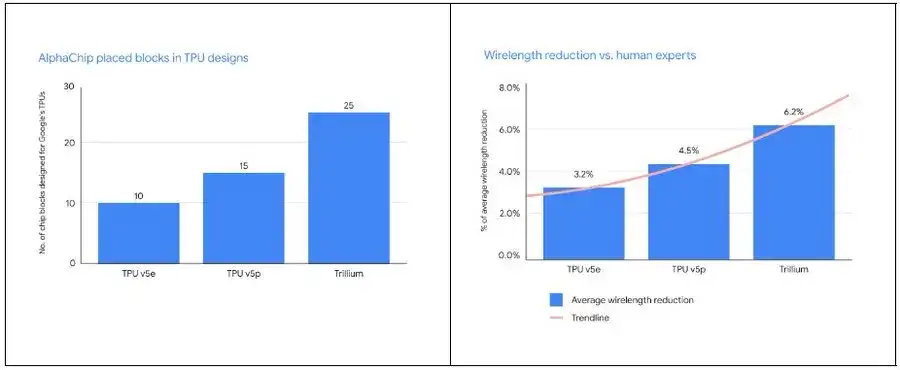

Heute wurde diese KI-gesteuerte Lernmethode auf mehreren Produktgenerationen getestet, darunter TPU v5e, TPU v5p und Trillium, und hat bei Google bemerkenswerte Ergebnisse erzielt. Noch bemerkenswerter ist, dass das Google DeepMind-Team kürzlich in Nature einen Anhang zu dieser Methode veröffentlicht hat, in dem die weitreichenden Auswirkungen auf den Bereich des Chipdesigns ausführlicher erläutert werden. gleichzeitig,Google hat außerdem einen vortrainierten Kontrollpunkt basierend auf 20 TPU-Modulen geöffnet, die Modellgewichte freigegeben und ihn AlphaChip genannt.

Das Aufkommen von AlphaChip zeigt nicht nur, dass die Anwendung von KI im Chipdesign umfangreicher werden wird, sondern markiert auch, dass wir uns auf eine neue Ära des „Chipdesigns“ zubewegen.

AlphaChip: Wie Google DeepMind mithilfe von KI das Chipdesign revolutioniert

Als Höhepunkt von Google DeepMind erregt AlphaChip mit seinen revolutionären Fortschritten im Chipdesign die Aufmerksamkeit der weltweiten Technologie-Community.

Chipdesign ist ein Spitzenfeld moderner Technologie. Seine Komplexität liegt in der geschickten Verbindung unzähliger Präzisionskomponenten durch extrem feine Drähte. Als eine der ersten Reinforcement-Learning-Technologien, die zur Lösung realer technischer Probleme eingesetzt werden, kann AlphaChip Chip-Layout-Designs in nur wenigen Stunden fertigstellen, die mit denen des Menschen vergleichbar oder sogar besser sind, ohne dass wochen- oder monatelange menschliche Arbeit erforderlich ist. Dieser bahnbrechende Fortschritt hat unserer Vorstellungskraft die Tür über traditionelle Grenzen hinaus geöffnet.

Wie genau schafft AlphaChip dieses Kunststück?

Das Geheimnis von AlphaChip liegt im angewandten Prinzip des bestärkenden Lernens, das den Entwurf des Chip-Layouts als Spiel behandelt. Ausgehend von einem leeren Raster platziert AlphaChip nach und nach alle Schaltungskomponenten, bis alle an ihrem Platz sind. Anschließend vergibt das System entsprechende Belohnungen basierend auf der Qualität des Layouts.

Noch wichtiger ist, dass Google auf innovative Weise ein „kantenbasiertes“ Graph-Neuralnetzwerk vorgeschlagen hat.Dadurch ist AlphaChip in der Lage, die Beziehungen zwischen Chipkomponenten zu erlernen und sie auf das Design des gesamten Chips anzuwenden, wodurch bei jedem Design eine Selbsttranszendenz erreicht wird. Ähnlich wie bei AlphaGo kann man mit AlphaChip durch „Spiele“ lernen, die Kunst des Entwerfens hervorragender Chip-Layouts zu meistern.

Im spezifischen Prozess der Gestaltung des TPU-Layouts wird AlphaChip zunächst verschiedene Module früherer Chipgenerationen vortrainieren, darunter On-Chip- und Inter-Chip-Netzwerkmodule, Speichercontroller und Datenübertragungspuffer. Diese Vortrainingsphase bietet AlphaChip umfangreiche Erfahrungen. Anschließend verwendete Google AlphaChip, um hochwertige Layouts für aktuelle TPU-Module zu generieren.

Im Gegensatz zu herkömmlichen Methoden optimiert sich AlphaChip kontinuierlich selbst, indem es weitere Chip-Layout-Aufgaben löst, genauso wie menschliche Experten ihre Fähigkeiten durch Übung verbessern. Wie DeepMind-Mitbegründer und CEO Demis Hassabis sagte:Google hat rund um AlphaChip eine leistungsstarke Feedbackschleife aufgebaut:

* Trainieren Sie zunächst ein erweitertes Chipdesignmodell (AlphaChip).

* Zweitens: Verwenden Sie AlphaChip, um bessere KI-Chips zu entwickeln

* Verwenden Sie dann diese KI-Chips, um bessere Modelle zu trainieren

* Verwenden Sie diese Modelle schließlich, um bessere Chips zu entwerfen

Dieser sich wiederholende Prozess ermöglicht die gleichzeitige Aktualisierung von Modellen und KI-Chips. Demis Hassabis sagte: „Dies ist einer der Gründe, warum der TPU-Stack von Google so gut funktioniert.“

Im Vergleich zu menschlichen Experten platziert AlphaChip nicht nur mehr Module, sondern reduziert auch die Verkabelungslänge erheblich.Mit jeder neuen TPU-Generation entwirft AlphaChip ein besseres Chip-Layout und bietet so einen vollständigeren Gesamtgrundriss, wodurch der Designzyklus verkürzt und die Chipleistung verbessert wird.

Die 10-jährige Reise von Google TPU: Von der ASIC-Beständigkeit zur KI-Designinnovation

Als Entdecker und Pionier auf dem TPU-Gebiet beruht Googles Entwicklungsgeschichte in diesem Technologiezweig nicht nur auf seinem scharfen Verstand, sondern zeugt auch von seinem außergewöhnlichen Mut.

Wie wir alle wissen, war in den 1980er JahrenASIC (Application Specific Integrated Circuit) zeichnet sich durch hohe Kosteneffizienz, starke Verarbeitungsleistung und hohe Geschwindigkeit aus.Es hat auf dem Markt große Zustimmung gefunden. Die Funktionalität eines ASIC wird jedoch durch benutzerdefinierte Maskentools bestimmt, was bedeutet, dass Kunden im Voraus hohe einmalige Entwicklungsgebühren (NRE) zahlen müssen.

zu diesem Zeitpunkt,FPGA (Field Programmable Gate Array) bietet den Vorteil niedrigerer Vorlaufkosten und geringerer Risiken bei der Anpassung der digitalen Logik.Es ist ins Blickfeld der Öffentlichkeit geraten und obwohl es in puncto Leistung nicht alle anderen Modelle übertrifft, ist es auf dem Markt einzigartig.

Damals ging man in der Branche allgemein davon aus, dass das Mooresche Gesetz die Leistung von FPGAs über die Anforderungen von ASICs hinaus steigern würde. Es stellt sich jedoch heraus, dass FPGA als programmierbarer „Universalchip“ in explorativen Produkten und Kleinserienprodukten gute Leistungen erbringt und eine bessere Geschwindigkeit, einen besseren Stromverbrauch oder bessere Kostenindikatoren als GPUs erreichen kann. Dennoch kann es sich der Regel nicht entziehen, dass „Universalität und Optimalität nicht gleichzeitig erreicht werden können“. Nachdem FPGAs den Weg für eine spezialisierte Architektur geebnet hatten, wurden sie durch spezialisiertere ASICs ersetzt.

Seit dem 21. Jahrhundert ist der Hype um KI-Technologie immer stärker geworden. Die Algorithmen für maschinelles Lernen und Deep Learning wurden ständig weiterentwickelt. Die Nachfrage der Branche nach leistungsstarken, stromsparenden dedizierten KI-Computerchips ist gestiegen, und CPUs, GPUs usw. scheinen mit vielen komplexen Aufgaben nicht fertig zu werden. Vor diesem Hintergrund traf Google 2013 eine mutige Entscheidung.Für den Aufbau der TPU-Infrastruktur und die Entwicklung rund um TensorFlow und JAX wurden ASICs ausgewählt.

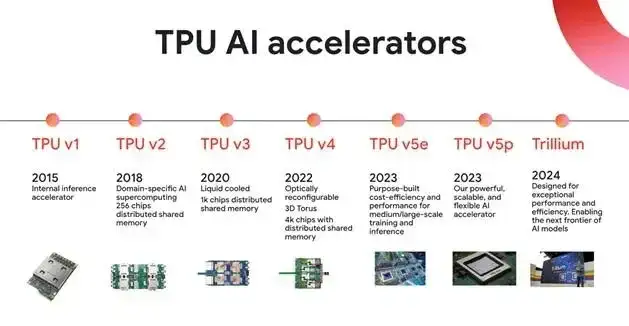

Es ist erwähnenswert, dass die unabhängige Forschung und Entwicklung von ASICs ein Prozess mit einem langen Zyklus, großen Investitionen, hohen Hürden und großem Risiko ist. Wird die falsche Richtung gewählt, kann dies zu enormen wirtschaftlichen Verlusten führen. Um jedoch kostengünstigere und energieeffizientere Lösungen für maschinelles Lernen zu erforschen, begann Google 2013 unmittelbar nach dem Durchbruch bei der Bilderkennung durch Deep Learning mit der Entwicklung von TPUv1 und kündigte 2015 die interne Markteinführung der ersten Generation von TPU-Chips (TPU v1) an.Dies markiert die Geburt des weltweit ersten Beschleunigers, der speziell für KI entwickelt wurde.

Glücklicherweise bot sich TPU bald eine eindrucksvolle Demonstrationsmöglichkeit – im März 2016 besiegte AlphaGo Lee erfolgreich den Go-Weltmeister Lee Sedol. Als Version der zweiten Generation der AlphaGo-Reihe läuft es auf Google Cloud und verbraucht 50 TPUs für Berechnungen.

Allerdings gelang es TPU nicht sofort, in großem Maßstab erfolgreich in der Industrie eingesetzt zu werden. Erst mit der Einführung der AlphaChip-Chip-Layoutmethode erreichte TPU wirklich eine neue Entwicklungsstufe.

Im Jahr 2020 demonstrierte Google die Fähigkeiten von AlphaChip in einem Preprint-Papier mit dem Titel „Chip Placement with Deep Reinforcement Learning“.Es kann aus vergangenen Erfahrungen lernen und sich kontinuierlich verbessern, indem es eine neuronale Architektur entwirft, die Belohnungen für eine Vielzahl von Netzlisten und deren Layouts genau vorhersagen kann und umfangreiche Feature-Einbettungen für die Eingabenetzliste generiert.

AlphaChip betrachtet die Bedingungen für die Leistungsoptimierung als Gewinnbedingungen des Spiels und verwendet die Methode des bestärkenden Lernens, um die Chip-Layout-Fähigkeiten kontinuierlich zu optimieren, indem ein intelligenter Agent trainiert wird, mit dem Ziel, die kumulativen Belohnungen zu maximieren. Sie führten 10.000 Spiele durch, bei denen die KI Layout und Routing auf 10.000 Chips üben und Daten sammeln konnte, während sie kontinuierlich lernte und optimierte.

Letztendlich stellten sie fest, dass KI im Vergleich zu menschlichen Ingenieuren hinsichtlich Fläche, Leistung und Kabellänge eine bessere oder vergleichbare Leistung wie das manuelle Layout erzielte und gleichzeitig die Designkriterien in deutlich kürzerer Zeit erfüllte. Die Ergebnisse zeigen, dassAlphaChip kann in weniger als 6 Stunden Layouts auf modernen Beschleuniger-Netzlisten generieren, die mit der manuellen Leistung mithalten oder diese übertreffen.Unter den gleichen Bedingungen könnten vorhandene menschliche Experten mehrere Wochen benötigen, um die gleiche Aufgabe zu erledigen.

Mithilfe von AlphaChip verstärkt Google seine Abhängigkeit von TPU. Dezember 2023Google hat drei verschiedene Versionen des multimodalen Allzweck-Großmodells Gemini auf den Markt gebracht, das in großem Umfang Cloud TPU v5p-Chips für das Training nutzt. Mai 2024Google hat den TPU-Chip Trillium der sechsten Generation herausgebracht, der in einem einzigen Pod mit hoher Bandbreite und geringer Latenz zu einem Cluster von bis zu 256 TPUs erweitert werden kann. Im Vergleich zu früheren Generationen ist Trillium bei der Anpassung des Modelltrainings leistungsfähiger.

Gleichzeitig haben TPU-Chips nach und nach auch außerhalb von Google Einzug gehalten und eine breitere Marktbekanntheit erlangt. 30. Juli 2024In einem von Apple veröffentlichten Forschungspapier behauptete das Unternehmen, dass es beim Training des AFM-Modells für künstliche Intelligenz im Apple Intelligence-Ökosystem zwei Arten von Tensor Processing Unit (TPU)-Cloud-Clustern von Google ausgewählt habe. Andere Daten zeigen, dass mehr als 601.000.000 generative KI-Startups und fast 901.000.000 generative KI-Einhörner die KI-Infrastruktur und Cloud TPU-Dienste von Google Cloud nutzen.

Alle Anzeichen deuten darauf hin, dass TPU nach einem Jahrzehnt harter Arbeit seine Inkubationsphase hinter sich gelassen hat und mit seiner hervorragenden Hardwareleistung beginnt, zum KI-Zeitalter von Google beizutragen.Der in AlphaChip enthaltene Lehrgang „KI-Design von KI-Chips“ hat auch im Bereich des Chipdesigns neue Horizonte eröffnet.

KI revolutioniert das Chipdesign: Vom Google AlphaChip zur Erforschung der vollständigen Prozessautomatisierung

Obwohl AlphaChip auf dem Gebiet der KI-entwickelten Chips einzigartig ist, ist das Unternehmen nicht allein. Die Tentakel der KI-Technologie wurden weitreichend auf viele wichtige Bereiche wie Chip-Verifizierung und -Tests ausgedehnt.

Die Kernaufgabe des Chipdesigns besteht darin, den Stromverbrauch (Power), die Leistung (Performance) und die Fläche (Area) des Chips zu optimieren. Diese drei Schlüsselindikatoren werden zusammen als PPA bezeichnet. Diese Herausforderung wird auch als Design Space Exploration bezeichnet. Traditionell wird diese Aufgabe von EDA-Tools erledigt, aber um eine optimale Leistung zu erzielen, müssen Chip-Ingenieure ständig manuelle Anpassungen vornehmen und diese dann zur Optimierung erneut an EDA-Tools übergeben und diesen Zyklus wiederholen. Dieser Vorgang ist vergleichbar mit dem Aufstellen von Möbeln in Ihrem Zuhause. Dabei versuchen Sie ständig, den Raum bestmöglich auszunutzen und den Verkehrsfluss zu optimieren. Jede Anpassung ist jedoch gleichbedeutend mit dem Herausrücken und Umstellen der Möbel, was äußerst zeit- und arbeitsintensiv ist.

Um dieses Problem zu lösen,Synopsys hat DSO.ai im Jahr 2020 eingeführt.Dies ist die erste Chipdesignlösung der Branche, die KI und EDA integriert. DSO.ai verwendet Reinforcement-Learning-Technologie, um den Designraum automatisch mithilfe von KI zu durchsuchen und ohne menschliches Eingreifen den besten Gleichgewichtspunkt zu finden. Dieses Tool wurde von mehreren Chip-Giganten verwendet.

Beispielsweise konnte Microsoft nach der Verwendung von DSO.ai den Stromverbrauch von Chipmodulen um 10%–15% senken und gleichzeitig die Leistung beibehalten. STMicroelectronics hat die Effizienz der PPA-Exploration um mehr als das Dreifache gesteigert; und der Speicherchip-Riese SK Hynix hat die Chipfläche um 5% reduziert. Daten von Synopsys zeigen, dass DSO.ai bei mehr als 300 kommerziellen Tape-Outs erfolgreich mitgewirkt hat, was darauf hindeutet, dass KI bei der Entwicklung und Produktion echter Chips eine wichtige Rolle spielt.

In Bezug auf die KI-gestützte Chipverifizierung wies ein von Synopsys veröffentlichter technischer Bericht auch darauf hin, dass der Verifizierungsprozess bis zu 70% des gesamten Chipentwicklungszyklus in Anspruch nimmt. Die Kosten für ein Chip-Tape-Out betragen Hunderte Millionen Dollar und die Komplexität moderner Chips nimmt ständig zu, sodass man sich vorstellen kann, wie schwierig die Verifizierung ist. zu diesem Zweck,Synopsys hat das Tool VSO.ai eingeführt.Verwenden Sie KI, um den Verifizierungsbereich zu optimieren und die Konvergenz der Abdeckung zu beschleunigen.

VSO.ai kann verschiedene Abdeckungstypen ableiten, um die herkömmliche Codeabdeckung zu ergänzen. Zudem kann KI aus Verifizierungserfahrungen lernen, um die Abdeckungsziele kontinuierlich zu optimieren. Darüber hinaus hat Synopsys das Tool TSO.ai auf den Markt gebracht, das Chipentwicklern dabei helfen kann, fehlerhafte Chips aus Gießereien auszusortieren.

Die starke Einbindung von KI in den Bereich des Chipdesigns hat eine kühne Idee hervorgerufen: Können wir KI nutzen, um einen kompletten Chip zu entwerfen? Tatsächlich hat Nvidia in diesem Bereich bereits Versuche unternommen. Entwerfen von Schaltkreisen durch Deep Reinforcement Learning Agents,Fast 13.000 Schaltkreise im H100 von Nvidia werden durch KI entworfen. Auch das Institut für Computertechnologie der Chinesischen Akademie der Wissenschaften nutzte KI, um innerhalb von 5 Stunden einen RISC-V-Prozessorchip namens „Erleuchtung Nr. 1“ zu entwickeln.Mit 4 Millionen Logikgattern ist seine Leistung mit der des Intel 80486 vergleichbar.

Insgesamt ist die Fähigkeit der KI, komplette Chips zu entwerfen, noch begrenzt, aber dies ist zweifellos eine wichtige Chance für die zukünftige Chipentwicklung. Mit der kontinuierlichen Weiterentwicklung der Technologie wird das Potenzial der KI im Bereich des Chipdesigns weiter erforscht und genutzt und wird letztendlich den gesamten Chipdesignprozess verändern.