Command Palette

Search for a command to run...

Google Dévoile Son Arme Secrète De TPU, AlphaChip Publiée Dans Nature ! Analyse Approfondie De l'historique Du Développement Des Puces De Conception d'IA

En 2020, Google a publié un article préliminaire historique intitulé « Chip Placement with Deep Reinforcement Learning », montrant au monde pour la première fois la disposition de sa puce conçue à l'aide d'une nouvelle méthode d'apprentissage par renforcement.Cette innovation a permis à Google d'introduire l'IA dans la conception de la puce TPU, obtenant ainsi une disposition de puce qui surpasse les concepteurs humains.

D'ici 2022, Google a rendu le code de l'algorithme décrit dans l'article encore plus open source, permettant aux chercheurs du monde entier d'utiliser cette ressource pour pré-entraîner des blocs de puces.

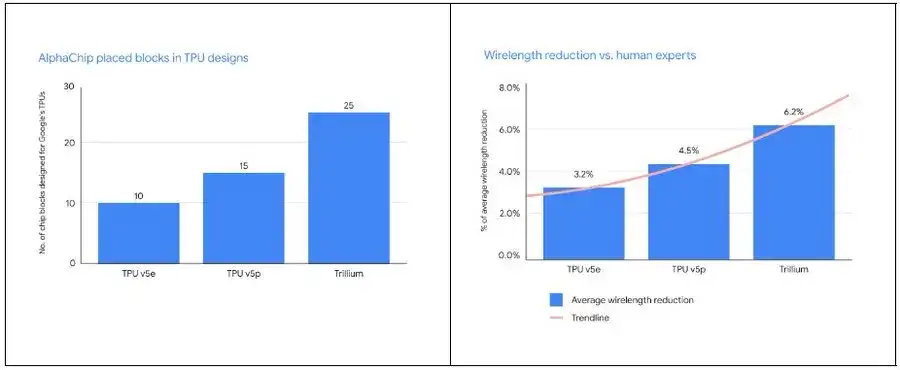

Aujourd’hui, cette méthode d’apprentissage basée sur l’IA a été testée sur plusieurs générations de produits, notamment TPU v5e, TPU v5p et Trillium, et a obtenu des résultats remarquables au sein de Google. Ce qui est encore plus frappant, c’est que l’équipe Google DeepMind a récemment publié une annexe à cette méthode dans Nature, qui détaille son impact considérable sur le domaine de la conception de puces. en même temps,Google a également ouvert un point de contrôle pré-entraîné basé sur 20 modules TPU, a partagé les poids du modèle et l'a nommé AlphaChip.

L'avènement d'AlphaChip indique non seulement que l'application de l'IA dans la conception de puces deviendra plus étendue, mais marque également que nous nous dirigeons vers une nouvelle ère de « conception de puces ».

AlphaChip : Comment Google DeepMind utilise l'IA pour révolutionner la conception des puces

En tant que sommet de Google DeepMind, AlphaChip capte l’attention de la communauté technologique mondiale avec ses progrès révolutionnaires dans la conception de puces.

La conception de puces est un domaine au sommet de la technologie moderne. Sa complexité réside dans la connexion astucieuse d’innombrables composants de précision à travers des fils extrêmement fins. En tant que l'une des premières technologies d'apprentissage par renforcement appliquées pour résoudre des problèmes d'ingénierie du monde réel, AlphaChip peut réaliser des conceptions de puces comparables ou supérieures à celles des humains en quelques heures seulement, sans nécessiter des semaines ou des mois de travail humain. Ces progrès révolutionnaires ont ouvert la porte à notre imagination au-delà des limites traditionnelles.

Alors, comment AlphaChip parvient-il exactement à cet exploit ?

Le secret d'AlphaChip réside dans le principe d'apprentissage par renforcement qu'il adopte, qui traite la conception de la disposition des puces comme un jeu. À partir d'une grille vierge, AlphaChip place progressivement chaque composant du circuit jusqu'à ce que tous soient en place. Par la suite, le système attribuera des récompenses correspondantes en fonction de la qualité de la mise en page.

Plus important encore, Google a proposé de manière innovante un réseau neuronal graphique « basé sur les bords ».Cela permet à AlphaChip d'apprendre les relations entre les composants de la puce et de les appliquer à la conception de la puce entière, réalisant ainsi une auto-transcendance dans chaque conception. Semblable à AlphaGo, AlphaChip peut apprendre à travers des « jeux » à maîtriser l'art de concevoir d'excellentes dispositions de puces.

Dans le processus spécifique de conception de la disposition TPU, AlphaChip effectuera d'abord un pré-entraînement sur divers modules de générations précédentes de puces, notamment des modules réseau sur puce et inter-puces, des contrôleurs de mémoire et des tampons de transfert de données. Cette phase de pré-formation offre à AlphaChip une expérience riche. Google a ensuite utilisé AlphaChip pour générer des mises en page de haute qualité pour les modules TPU actuels.

Contrairement aux méthodes traditionnelles, AlphaChip s'optimise en permanence en résolvant davantage de tâches de conception de puces, tout comme les experts humains améliorent leurs compétences grâce à la pratique. Comme l'a déclaré Demis Hassabis, cofondateur et PDG de DeepMind :Google a construit une puissante boucle de rétroaction autour d'AlphaChip :

* Tout d’abord, formez un modèle de conception de puce avancé (AlphaChip)

* Deuxièmement, utilisez AlphaChip pour concevoir de meilleures puces d’IA

* Ensuite, utilisez ces puces d’IA pour former de meilleurs modèles

* Enfin, utilisez ces modèles pour concevoir de meilleures puces

Ce processus répétitif permet la mise à niveau simultanée des modèles et des puces d’IA. Demis Hassabis a déclaré : « C'est en partie la raison pour laquelle la pile TPU de Google fonctionne si bien. »

Par rapport aux experts humains, AlphaChip place non seulement plus de modules, mais réduit également considérablement la longueur du câblage.À chaque nouvelle génération de TPU, AlphaChip conçoit une meilleure disposition des puces, offrant un plan d'étage global plus complet, raccourcissant ainsi le cycle de conception et améliorant les performances des puces.

Le parcours de 10 ans de Google TPU : de la persistance ASIC à l'innovation en matière de conception d'IA

En tant qu'explorateur et pionnier dans le domaine du TPU, l'histoire du développement de Google dans cette ligne technologique repose non seulement sur sa perspicacité, mais démontre également son courage extraordinaire.

Comme nous le savons tous, dans les années 1980,L'ASIC (Application Specific Integrated Circuit) se caractérise par sa rentabilité élevée, sa forte puissance de traitement et sa vitesse élevée.Il a gagné une grande popularité sur le marché. Cependant, la fonctionnalité d'un ASIC est déterminée par des outils de masquage personnalisés, ce qui signifie que les clients doivent payer des frais d'ingénierie non récurrents (NRE) initiaux coûteux.

à ce moment-là,Le FPGA (Field Programmable Gate Array) présente l’avantage de réduire les coûts initiaux et de réduire les risques liés à la personnalisation de la logique numérique.Il est devenu célèbre et, même s'il ne surpasse pas tous les autres modèles en termes de performances, il est unique sur le marché.

À l’époque, l’industrie prévoyait généralement que la loi de Moore permettrait d’améliorer les performances des FPGA au-delà des besoins des ASIC. Mais il s'avère que le FPGA, en tant que « puce universelle » programmable, fonctionne bien dans les produits exploratoires et en petits lots et peut atteindre de meilleurs indicateurs de vitesse, de consommation d'énergie ou de coût que les GPU, mais il ne peut toujours pas échapper à la règle selon laquelle « l'universalité et l'optimalité ne peuvent pas être atteintes en même temps ». Une fois que les FPGA ont ouvert la voie à une architecture spécialisée, ils ont cédé la place à des ASIC plus spécialisés.

Depuis le 21e siècle, l’engouement pour la technologie de l’IA ne cesse de croître. Les algorithmes d’apprentissage automatique et d’apprentissage profond ont continué à évoluer. La demande de l'industrie en puces informatiques dédiées à l'IA hautes performances et à faible consommation d'énergie a augmenté, et les processeurs, les GPU, etc. semblent incapables de faire face à de nombreuses tâches complexes. Dans ce contexte, Google a pris une décision audacieuse en 2013.Les ASIC ont été choisis pour construire l'infrastructure TPU et se développer autour de TensorFlow et JAX.

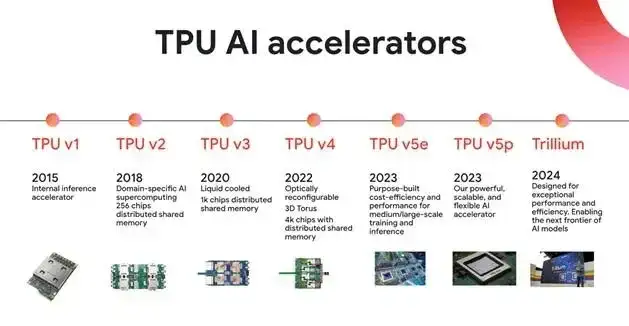

Il convient de noter que la recherche et le développement indépendants d'ASIC sont un processus avec un cycle long, un investissement important, un seuil élevé et un risque élevé. Une fois la mauvaise direction choisie, cela peut entraîner d’énormes pertes économiques. Cependant, afin d'explorer des solutions d'apprentissage automatique plus rentables et plus économes en énergie, Google a commencé à développer TPUv1 en 2013, immédiatement après avoir réalisé une percée dans la reconnaissance d'images grâce à l'apprentissage profond en 2012, et a annoncé le lancement interne de la première génération de puces TPU (TPU v1) en 2015.Cela marque la naissance du premier accélérateur au monde conçu spécifiquement pour l’IA.

Heureusement, TPU a rapidement eu l'occasion de faire une démonstration frappante : en mars 2016, AlphaGo Lee a battu avec succès le champion du monde de Go Lee Sedol. En tant que version de deuxième génération de la série AlphaGo, elle fonctionne sur Google Cloud et consomme 50 TPU pour les calculs.

Cependant, le TPU n’a pas immédiatement connu de succès à grande échelle dans l’industrie. Ce n’est que lorsque la méthode de conception de la puce AlphaChip a été proposée que le TPU est véritablement entré dans une nouvelle étape de développement.

En 2020, Google a démontré les capacités d’AlphaChip dans un article préliminaire intitulé « Chip Placement with Deep Reinforcement Learning ».Il est capable d'apprendre de l'expérience passée et de s'améliorer continuellement en concevant une architecture neuronale capable de prédire avec précision les récompenses sur une variété de listes de réseaux et leurs dispositions, générant des intégrations de fonctionnalités riches pour la liste de réseaux d'entrée.

AlphaChip considère les conditions d'optimisation des performances comme les conditions gagnantes du jeu et adopte la méthode d'apprentissage par renforcement pour optimiser en permanence les capacités de disposition des puces en formant un agent intelligent dans le but de maximiser les récompenses cumulatives. Ils ont lancé 10 000 jeux, permettant à l'IA de pratiquer la disposition et le routage sur 10 000 puces et de collecter des données, tout en apprenant et en optimisant en permanence.

En fin de compte, ils ont constaté que l’IA était plus performante ou comparable à la disposition manuelle en termes de surface, de puissance et de longueur de fil par rapport aux ingénieurs humains, tout en répondant aux critères de conception en beaucoup moins de temps. Les résultats montrent queAlphaChip peut générer des mises en page sur des listes de réseaux d'accélérateurs modernes qui rivalisent ou dépassent les performances manuelles en moins de 6 heures.Dans les mêmes conditions, les experts humains existants peuvent avoir besoin de plusieurs semaines pour accomplir la même tâche.

Avec l'aide d'AlphaChip, la dépendance de Google au TPU augmente. Décembre 2023Google a lancé trois versions différentes du grand modèle multimodal à usage général Gemini, qui utilise largement les puces Cloud TPU v5p pour la formation. Mai 2024Google a lancé la puce TPU de sixième génération Trillium, qui peut être étendue à un cluster de 256 TPU maximum dans un seul pod à bande passante élevée et à faible latence. Par rapport aux générations précédentes, Trillium est plus puissant dans l’adaptation de la formation des modèles.

Dans le même temps, les puces TPU ont progressivement dépassé Google et ont acquis une plus grande reconnaissance sur le marché. 30 juillet 2024Dans un document de recherche publié par Apple, la société a affirmé avoir sélectionné deux types de clusters cloud Tensor Processing Unit (TPU) de Google lors de la formation du modèle d'intelligence artificielle AFM dans l'écosystème Apple Intelligence. D'autres données montrent que plus de 60% de startups d'IA générative et près de 90% de licornes d'IA générative utilisent l'infrastructure d'IA de Google Cloud et les services Cloud TPU.

Tout indique qu'après une décennie de travail acharné, TPU est sorti de sa période d'incubation et commence à contribuer à l'ère de l'IA de Google avec ses excellentes performances matérielles.Le parcours « Conception de puces IA » contenu dans AlphaChip a également ouvert de nouveaux horizons dans le domaine de la conception de puces.

L'IA révolutionne la conception des puces : de Google AlphaChip à l'exploration de l'automatisation complète des processus

Bien qu’AlphaChip soit unique dans le domaine des puces conçues par l’IA, il n’est pas seul. Les tentacules de la technologie de l’IA ont été largement étendus à de nombreux maillons clés tels que la vérification et les tests des puces.

La tâche principale de la conception des puces est d'optimiser la consommation d'énergie (Power), les performances (Performance) et la surface (Area) de la puce. Ces trois indicateurs clés sont collectivement appelés PPA. Ce défi est également appelé exploration de l’espace de conception. Traditionnellement, cette tâche est réalisée par des outils EDA, mais pour obtenir des performances optimales, les ingénieurs en puces doivent constamment effectuer des ajustements manuels, puis les transmettre à nouveau aux outils EDA pour optimisation, et répéter ce cycle. Ce processus est similaire au placement de meubles dans votre maison, en essayant constamment de maximiser l'utilisation de l'espace et d'optimiser la circulation, mais chaque ajustement équivaut à déplacer les meubles et à les réorganiser, ce qui prend énormément de temps et demande beaucoup de travail.

Afin de résoudre ce problème,Synopsys a lancé DSO.ai en 2020.Il s’agit de la première solution de conception de puces du secteur qui intègre l’IA et l’EDA. DSO.ai utilise la technologie d'apprentissage par renforcement pour rechercher automatiquement l'espace de conception via l'IA afin de trouver le meilleur point d'équilibre sans intervention humaine. Cet outil a été utilisé par plusieurs géants des puces électroniques.

Par exemple, après avoir utilisé DSO.ai, Microsoft a réduit la consommation d’énergie des modules de puce de 10% à 15% tout en maintenant les performances ; STMicroelectronics a augmenté l'efficacité de l'exploration PPA de plus de 3 fois ; et le géant des puces mémoire SK Hynix a réduit la surface de la puce de 5%. Les données de Synopsys montrent que DSO.ai a contribué avec succès à plus de 300 sorties de bandes commerciales, ce qui indique que l'IA joue un rôle important dans la conception et la production de puces réelles.

En termes de vérification des puces assistée par l'IA, un rapport technique publié par Synopsys a également souligné que le processus de vérification prend jusqu'à 70% de l'ensemble du cycle de développement de la puce. Le coût d'une bande magnétique peut atteindre des centaines de millions de dollars, et la complexité des puces modernes continue d'augmenter, de sorte que la difficulté de la vérification peut être imaginée. à cette fin,Synopsys a lancé l'outil VSO.ai.Utilisez l’IA pour optimiser l’espace de vérification et accélérer la convergence de la couverture.

VSO.ai peut déduire différents types de couverture pour compléter la couverture de code traditionnelle, et l'IA peut également apprendre de l'expérience de vérification pour optimiser en permanence les cibles de couverture. En outre, Synopsys a également lancé l'outil TSO.ai, qui peut aider les développeurs de puces à éliminer les puces défectueuses fabriquées par les fonderies.

L’implication profonde de l’IA dans le domaine de la conception de puces a déclenché une idée audacieuse : pouvons-nous utiliser l’IA pour concevoir une puce complète ? En fait, Nvidia a déjà fait des tentatives dans ce domaine. Conception de circuits grâce à des agents d'apprentissage par renforcement profond,Près de 13 000 circuits du H100 de Nvidia sont conçus par l'IA. L'Institut de technologie informatique de l'Académie chinoise des sciences a également utilisé l'IA pour générer une puce de processeur RISC-V appelée « Enlightenment No. 1 » en 5 heures.Avec 4 millions de portes logiques, ses performances sont comparables à celles de l'Intel 80486.

Dans l’ensemble, la capacité de l’IA à concevoir des puces complètes est encore limitée, mais il s’agit sans aucun doute d’une opportunité importante pour le développement futur des puces. Avec les progrès continus de la technologie, le potentiel de l’IA dans le domaine de la conception de puces sera davantage exploré et utilisé, et changera finalement l’ensemble du processus de conception de puces.